| GHDL (0.29-r8) | 2010-01-30 11:59 |

| Icarus Verilog (0.9.2-r19) | 2010-09-03 20:10 |

波形表示は後回しにするとして、ModelSimと同じことをIcarus Verilogでやろうとすると、

iverilog -I ../ecc/source -s ecc_tb -o ecc_tb.out \ ../ecc/source/ecc_top.v ../ecc/source/ecc_encoder.v ../ecc/source/ecc_decoder.v ../ecc/testbench/ecc_tb.v vvp -n ecc_tb.outとなります。iverilogコマンドの解説、vvpコマンドも参考にしてください。

出力は以下のようになるはずです。Atom Z560 2.13Ghzを搭載したPCで、完了まで約38秒かかりました。

TESTING CAPABILITY TO DETECT AND CORRECT ONE BIT ERROR TESTING CAPABILITY TO DETECT TWO BIT ERRORS ALL TESTS COMPLETED SUCCESSFULLY

エディタで下記の内容のテキストファイルを作り、WAVEDUMP.vという名前で保存してください。$dumpvarsの第一引数は英字のオーでなく数字のゼロですので注意。

`timescale 1 ps / 1 ps

module WAVEDUMP;

initial begin

$dumpfile("ecc_tb.vcd");

$dumpvars(0, ecc_tb);

end

endmodule

そして、iverilogのオプションに-s WAVEDUMPとWAVEDUMP.vを加えます。

iverilog -I ../ecc/source -s ecc_tb -s WAVEDUMP -o ecc_tb.out \ WAVEDUMP.v ../ecc/source/ecc_top.v ../ecc/source/ecc_encoder.v ../ecc/source/ecc_decoder.v ../ecc/testbench/ecc_tb.v vvp -n ecc_tb.outこのときWAVEDUMP.vは、Verilogソースの羅列の最後尾ではなく一番最初に書いてください。 モジュールに`timescaleの指定が含まれていない場合iverilogは#1を1秒と解釈するので、`timescale指定を含むWAVEDUMP.vが一番最初にこないと、見づらい波形ファイルができてしまいます。

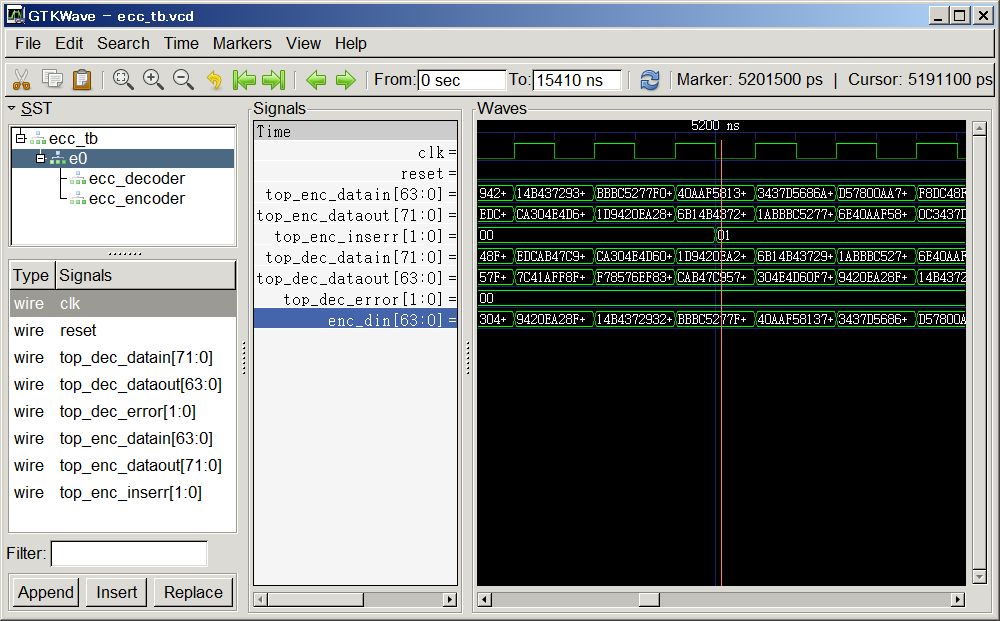

vvpを実行した結果としてecc_tb.vcdが出力されます。gtkwaveで波形を表示することができます。

gtkwave ecc_tb.vcd